## LECTURE NOTES (E- CONTENTS) for

**B.Sc. II Electronics (2021-22)**

Semester – III, Paper - III

DSC -1005 C:

# **Electronics Communication and Microprocessor 8085**

**Section-II Microprocessor 8085**

Unit- I: Microcomputer Organization

As per the syllabus of

Vivekanand College (Autonomous), Kolhapur

Prepared and Circulated

for B.Sc.II Electronics Students

by

Dr. C. B. Patil

Assistant Professor, Department of Electronics

Vivekanand College (Autonomous), Kolhapur

(For Private Circulation only)

## Unit –I

**Microcomputer Organization**

#### Introduction:

Microcomputer is a small, relatively inexpensive computer with a microprocessor as its central processing unit (CPU). It includes a microprocessor, memory, and minimal input/output (I/O) circuitry mounted on a single printed circuit board. Microcomputer is designed for individual use and is smaller in size than a mainframe or a minicomp uter. We now refer to microcomputers as, simply, computers, or personal computers (PC). Desktop computers, laptops, personal digital assistant (PDA), tablets & Smartphones are all types of microcomputers.

#### **Organization of Microcomputer:-**

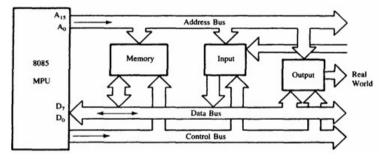

A structure of **Microcomputer** (microprocessor based system) is as shown in fig1.1. It includes mainly four parts- i) Microprocessor ii) Memory iii) Input unit iv) Output unit

Fig.1.1 Basic Microcomputer system

**Microprocessor:** Microprocessor is a multipurpose, programmable logical device that reads binary instructions from memory, accepts binary data as an input & processes the data according to those instructions and provides the result as an output.

Microprocessor ( $\mu$ P) is a semiconductor device consisting of several digital circuits, which performs together to execute the instructions given by the user. Depending upon the capability of handling a data, they are classified as 4-bit, 8-bit, 16-bit, 32-bit, 64-bit microprocessors.

Basically microprocessor has 3 minimum components:

a) ALU [Arithmetic Logical Unit]:-In this area of microprocessor, various computing functions are performed on data. It performs arithmetic operations as well as logical operations.

b) Register Array :-It consists of various registers. These registers are primary used to store the data temporarily during the execution of the program.

c) Control unit [CU]: - provides the necessary timing & control signals to all the operations in the microprocessor system.

#### 1 Evolution of the Microprocessors:

**1st Generation:** This was the period during 1971 to 1973 of microprocessor's history. The first  $\mu$ P was introduced in 1971 by Intel (Integrated Electronics) Corporation. This was the Intel 4004, a processor on a single chip. It had the capability of performing simple arithmetic and logical operations. For example, addition, subtraction, comparison, logical AND and OR operations. It also had a control unit which could perform various control functions like fetching an instruction from the memory, decoding it and generating control signals to execute it. During this period, the other microprocessors were launched in the market such as Rockwell international PPS-4, INTEL-8008 and National semiconductors IMP-16. INTEL-8008 was the first 8 bit  $\mu$ P, which would perform arithmetic and logic operations on 8 bit words, was introduced in 1973, by Intel. Then its improved version- INTEL 8080 was introduced.

The First generation microprocessors were designed using the PMOS (P-channel Metal Oxide Semiconductor) technology. This technology was cost effective, but with slow device speed, low output currents and compatible only with TTL family.

**2<sup>nd</sup> Generation:** This was the period during 1973 to 1978 in which very efficient 8-bit microprocessors were implemented like INTEL-8085, Motorola 6800 and 6801 and Zilogs-Z80, which were among the most popular ones. Owing to their superfast speed, they were costly as they were based on NMOS (N-channel MOS) technology fabrication.

**3rd Generation:** During this period 16 bit processors were designed using HMOS (Highperformance n-channel Metal Oxide Semiconductor) technology. From 1979 to 1980, INTEL 8086/80186/80286 and Motorola 68000 and 68010 were introduced. Speeds of those processors were four times better than the 2nd generation processors. Later, Intel introduced a high speed version of the 8085A called 8085AH using HMOS technology. One of the most popular 16-bit µP introduced by Intel was 8088. The 8088 has the same instruction set as the 8086. However, it has only an 8 bit data bus. The 8088 was the µP used in the IBM PC and its clones.

**4th Generation:** From 1981 to 1995 this generation developed 32 b it microprocessors by using HCMOS (High-performance Complementary Metal Oxide Semiconductor) fabrication. INTEL-80386/80486, Motorola's 68020/68030/68040 and National semiconductor NS 32032 were the popular processors. These microprocessors have on-chip RAM called the **cache memory** to speed up program execution.

**5th Generation:** From 1995 to until now this generation has been bringing out highperformance and high-speed processors that make use of 64 -bit processors. Such processors include Pentium, Celeron, Dual and Quad core processors.

Thus, microprocessor has evolved through all these generations, and the fifth generation microprocessors represent advancement in specifications as shown in Table 1.1.

|                             | 4004     | 8008    | 8085A   | 8086     | 80386    |

|-----------------------------|----------|---------|---------|----------|----------|

| Year of<br>Introduction     | 1971     | 1971    | 1977    | 1978     | 1985     |

| Data Bus                    | 4-bit    | 8-bit   | 8-bit   | 16-bit   | 32-bit   |

| Technology                  | PMOS     | PMOS    | NMOS    | HMOS     | CHMOS    |

| Word size data/ instr.      | 4/8      | 8/8     | 8/8     | 16/16    | 32/32    |

| Address<br>capacity         | 4K       | 16K     | 64K     | 1M       | 4G       |

| Clock<br>kHz/phase          | 740/2    | 800/2   | 6250/2  | 8000/2   | 16000/2  |

| Addition time               | 10.8 µs  | 20 µs   | 1.3 µs  | 0.375 µs | 0.125 µs |

| ALU/General<br>Purpose Reg. | 1/16     | 1/6     | 1/6     | 1/8      | 1/8      |

| Stack size                  | 3x12     | 7x14    | RWM     | RWM      | RWM      |

| Voltages                    | 15-10,5* | -9.5v   | +5V     | +5V      | +5V      |

| Package size                | 16pin    | 18pin   | 40pin   | 40pin    | 132pin   |

| Instructions                | 45       | 48      | 74      | 133      | 135      |

| Transistors                 | 2,300    | 2,000   | 6,200   | 29,000   | 2,75,000 |

| Chip size(mil)              | 117x159  | 125x170 | 164x222 | 225x230  | 390x390  |

Table 1.1: Evaluation of major µP characteristics from Intel

**2 Applications of Microprocessors:** The application of microprocessors is increasing day by day. It is used in two different ways.

1. as a programmable logic device to control the process.

e.g - in home appliances, wireless communication equipments, office publication and automation, consumer electronic goods, calculators, accounting system, video games, industrial controllers and data acquisition systems.

2. as a data processing unit or a computing units of a computer like Desktop computers, laptops.

#### Memory: -

Memory is an essential component in microprocessor based systems, because it is necessary to store program/ instructions and data. The semiconductor memories are of two types ROM and RAM. ROM is a non-Volatile memory while RAM is Volatile memory. To store program/instructions, the system should have permanent (non-Volatile) memory, because program should not get erased due to any reason. It should remain intact even if power supply is switched off. Such a memory is called as "Program Memory". Its examples are EPROM or Flash memories. Now- a- days flash memories are most widely used. Also system should require another type of memory to store data temporarily. So once data is used, it can be over written by

new data. Thus we use this memory as "scratch pad". Such a memory is also called as "Data Memory". Its examples are SRAM (Static RAM) and DRAM (Dynamic RAM).

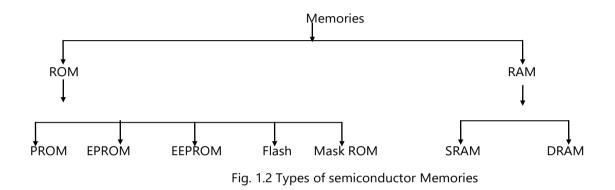

Basically information is stored in the form of binary numbers in semiconductor memories. As soon as CPU starts, it will first communicate with these memories. Hence semiconductor memories are referred as primary memory. Various types of semiconductor memories are as shown in fig.1.2.

**<u>1 ROM (Read-only memory)</u>**: ROM is a type of memory that does not lose its contents when the power is turned off, hence ROM is called *nonvolatile memory*. There are different types of read-only memory. They are PROM, EPROM, EEPROM, flash and masked ROM.

i. **PROM (Programmable Read only Memory):** In a PROM for every bit there exist a fuse. PROM is programmed by blowing the fuses. Once the fuses are burned we can't change data hence PROM is some time known as OTP (One time programmable)

#### ii EPROM (Erasable Programmable Read only Memory) :

Widely used EPROM is UV-EPROM i.e. Ultra-Violet Erasable Programmable Read Only Memory. This memory IC have a quartz window on it. When this IC is exposed with ultra violet light through this window for about 15 to 20 minutes then all the contents of this memory are erased. Upon erasing it can be reprogrammed by using EPROM programmer. Such ICs has a part number 27XX. e.g. 27128 where 27 refers UV -EPROM with capacity 128 K bits or 16 K bytes. The program/erase cycle for EPROM is 1,000 times.

Disadvantages : 1) It can't be programmed when it is in system board.

2) Single bit or byte can't be erased.

EEPROM or E<sup>2</sup>PROM: (Electrically Erasable Programmable Read Only Memory): This is similar to EPROM except that the erasing is done by electrical signals instead of UV light. Advantage of EEPROM is it can be erased and reprogrammed without removing it from board. Its single location can be erased. The program/erase cycle for EPROM is 1,00,000 times.

- iv. **Flash EPROM**: Now a days this is most popular Erasable Programmable ROM. It is widely used in mobile card, camera, even hard disk of computer. It is similar to EEPROM, but with small electrical pulse or flash (less than 1 sec.) all contents of memory are erased. This memory can be reprogrammed while it is in its socket. The program/erase cycle for flash is 1,00,000 times.

- v. <u>Mask ROM</u>: Contents or data on this ROM is programmed by IC manufacturer; hence it is not user-programmable ROM. It is costly and used only when large quantity is required.

#### 2 RAM (Random access Memory):

RAM is type of memory that loses its contents when power is turned off, hence RAM is called *volatile memory*; sometimes it is also called as Read-write memory. There are two types of RAMs, 1) SRAM and 2) DRAM.

i. **SRAM** (Static RAM): In this type of memory 1 or 0 are stored on memory cell in the form of voltage. Memory cell is constructed using flip-flop and each flip-flop requires about 6 transistors, so such memories are bulky.

### ii. DRAM(Dynamic RAM):

In this type of memory, data (i.e.1 and 0) is stored in the form of charge on capacitor instead of voltage. Because of this number of transistors required to store data are reduced as compare to static RAM. Due to this size of memory cell is also reduced. However this type of memory requires constant refreshing due to leakage of charge on capacitor.

#### 3 Memory structure and its requirements:

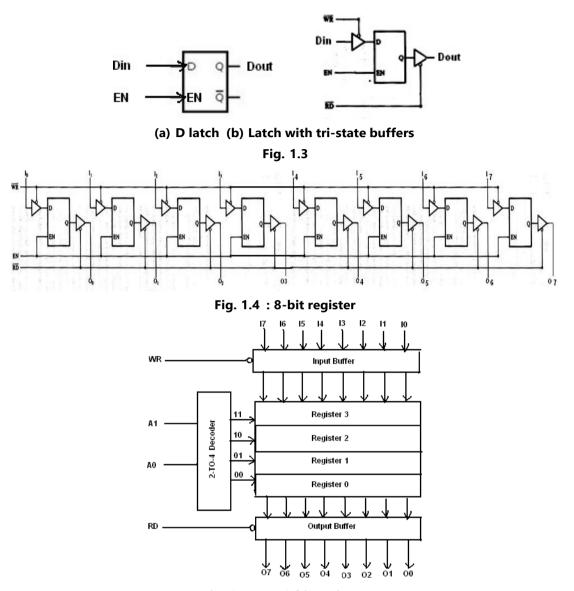

A flip-flop or latch is a basic element of memory. To write or store a bit in the latch, an input data pin Din and enable signal (EN) is required as shown in Fig. 1.3(a). In this latch the stored bit is always available on the output line Dout. To avoid unintentional change in the input and to control the availability of the output, tri-state buffers are used as shown in fig. 1.3(b).Thus we can write into the latch by enabling the input buffer and read from it by enabling the output buffer. This latch is called as a memory cell. Fig. 1.4 shows eight such cells grouped together to form a register. The size of this register is specified as 8-bit or  $1 \times 8$  bit. Such registers are grouped together to form a memory. In Fig. 1.5, four registers with eight cells are arranged in a sequence. To write into or read from any one of the registers, a specific register should be identified or enabled. This is done by 2-to-4 decoder. However two more lines A1 and A0 called as address lines are required to the decoder. These two input lines can have four different bit combinations (00, 01, 10, 11) and each combination can identify or enable one of the registers named as Register 0 through Register 3. Thus the enable signal of the flip flop in Fig. 1.4 is replaced by two address lines in fig. 1.5. In this way we can expand number of registers. If we have eight registers on one chip, we need three address lines and if we have 16 registers, we need four address lines.

Fig. 1.5 :  $4 \times 8$ -bit register

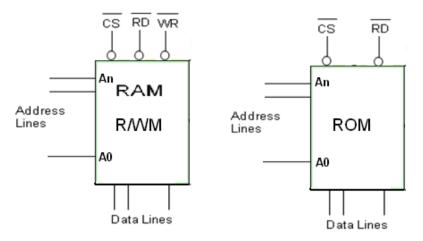

## Pin connections to memory devices:

- (i) Address connections : All memory devices have address inputs that select a memory location within the memory device. Address inputs are labelled from A0 to An.

- (ii) Data connections : All memory devices have a set of data outputs or input/outputs.

- (iii) Selection connection : Each memory device has an input that selects or enables the memory device. This kind of input is most often called a chip select ( $\overline{CS}$ ), chip enable ( $\overline{CE}$ ) or simply select ( $\overline{S}$ ) input.

- (iv) Control connections : A ROM usually has only one control input, while a RAM often has one or two control inputs. The control input most often found on the ROM is the output enable  $(\overline{OE})$  or gate( $\overline{G}$ ), this allows data to flow out of the output data pins of the ROM. A RAM has two control inputs, they are usually labelled  $\overline{WE}$  (write enable) or  $\overline{WR}$  and  $\overline{OE}$  (output enable) or  $_{R}$ .

A model of a typical memory chips representing above requirements is shown in Fig. 1.6.

#### (a) R/W Memory model

(b) ROM Memory model

## Fig. 1.6

Table 1.2 shows required address lines for memories of different capacities.

| Memory capacity              | Address lines required                |  |  |  |

|------------------------------|---------------------------------------|--|--|--|

| 1k = 1024 memory locations   | 10 (A <sub>0</sub> -A <sub>9</sub> )  |  |  |  |

| 2k = 2048 memory locations   | 11 (A <sub>0</sub> -A <sub>10</sub> ) |  |  |  |

| 4k = 3096 memory locations   | 12 (A <sub>0</sub> -A <sub>11</sub> ) |  |  |  |

| 8k = 8192 memory locations   | 13 (A <sub>0</sub> -A <sub>12</sub> ) |  |  |  |

| 16k = 16384 memory locations | 14 (A <sub>0</sub> -A <sub>13</sub> ) |  |  |  |

| 32k = 32768 memory locations | 15 (A <sub>0</sub> -A <sub>14</sub> ) |  |  |  |

| 64k = 65536 memory locations | 16 (A <sub>0</sub> -A <sub>15</sub> ) |  |  |  |

| Table | 1.2 : | Summari zes | capacity | of | memory | and | required | address | lines |

|-------|-------|-------------|----------|----|--------|-----|----------|---------|-------|

|       |       |             |          |    |        |     |          |         |       |

Some of EPROM ICs are:

2732 : In this IC 27 indicates it is EPROM and 32 belong to 8 bit data on each location and totally 4k locations ( $8 \times 4k = 32$ ) hence this IC is of 4 kbyte.

2764 : In this IC 27 indicates it is EPROM and 64 belong to 8 bit data on each location and totally 8k locations ( $8 \times 8k = 64$ ) hence this IC is of 8 kbyte.

27128 : In this IC 27 indicates it is EPROM and 128 belong to 8 bit data on each location and totally 16k locations ( $8 \times 16k = 128$ ) hence this IC is of 16 kbyte.

The memory handling capacity of a microprocessor depends on its address lines. The 8085, with its sixteen address lines can access 216 i.e. 64 K bytes of memory. Thus placing available memory chip within 64 K bytes address range is referred as 'memory Interfacing' or 'memory mapping'.

#### **4 EPROM INTERFACING**

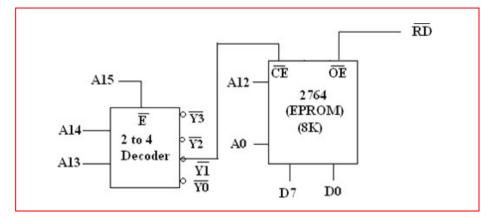

i) Interfacing EPROM 2764 memory chip

Fig. 1.7 : Interfacing of EPROM 2764 with 8085 microprocessor

Fig. 1.7 shows that interfacing of EPROM 2764 memory chip with 8K registers. The memory chip requires 13 address lines A0-A12 to identify 8K registers. The remaining address lines A13-A15 are connected to the 2 to 4 decoder. The decoder is enabled by A15 address line. The signal on A15 line  $\vec{E}$  should be low, because enable pin  $\vec{E}$  is active low. A13 and A14 address lines are the inputs to the 2 to 4 decoder. The output  $\vec{Y}_1$

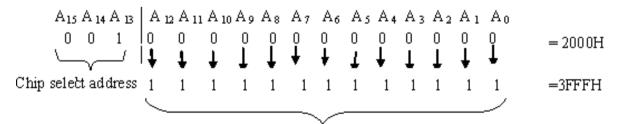

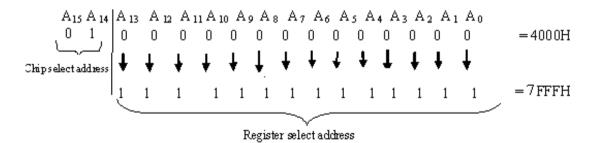

The memory chip is selected only when the address on A15A14A13 = 001. A15 enables the decoder and inputs A14A13 = 01, activates the output  $\overline{Y_1}$ . Once the chip is selected, the remaining address lines A0-A12 have any possible logic combinations between all 0s to all 1s to select one of the memory location or memory register from 8 K registers. Thus memory map of this chip will be,

Register select address

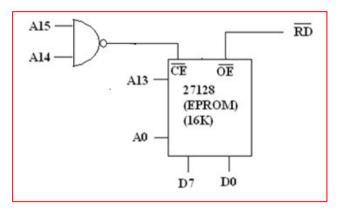

## ii) Interfacing of EPROM 27128 memory chip using NAND gate as Decoder

Fig. 1.8 : Interfacing of EPROM 2764 using NAND gate as decoder

The memory chip is selected only when the address on A15A14 = 11. The remaining address lines A0-A13 are used to identify any one of the registers. The address lines A0-A13 can have any possible logic combinations between all 0s to all 1s to select one of the memory location or memory register from 16 K registers. Thus memory map of this chip will be,

Register select address

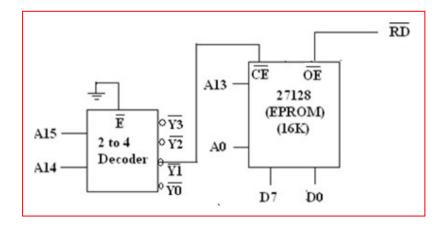

iii) Interfacing of EPROM 27128 memory chip using Decoder IC

Fig. 1.9 : Interfacing of EPROM 2764 using decoder IC

Fig. 1.9 shows that interfacing of EPROM 27128 memory chip with 16K registers. The memory chip requires 14 address lines A0-A13 to identify 16K registers. The remaining address lines A14-A15 are connected to the 2 to 4 decoder. As the decoder enable pin is active low, so that it is connected to ground. The address lines A14 and A15 are worked as inputs of 2 to 4 decoder. The output is  $\overline{Y_1}$  connected to  $\overline{CE}$  (chip enable) pin of memory chip. The  $\overline{RD}$  signal of 8085 microprocessor is directly connected  $\overline{OE}$  (Output Enable) pin of memory chip.

The memory chip is selected only when the address of A15A14 = 01; which activates the output  $\overline{Y_1}$ . Once, the chip is selected, the remaining address lines A0-A13 are used to identify any one of the registers. The address lines A0-A13 have any possible logic combinations between all 0s to all 1s. Thus memory map of this chip will be,

**Input unit:-** This section supplies the data and instructions in binary form to the system. e.g.-keyboard.

**1.2.4. Output Unit:-** This section transfers the data from microprocessor to the O/P devices such as 7-segment display, CRT screen, printer etc.

**Address Bus:-** It is unidirectional bus which carries addresses from microprocessor to peripheral devices.

Data Bus:- It is a bidirectional bus which transfers the data between microprocessor and peripherals.

10 | Page

Unit I: Microcomputer Organization

**Control Bus:-** Control bus consists of control signals which are given out by control unit of microprocessor to peripheral.

## Exercise

## Q. Select most correct alternative:

1) Microcomputer system is built using-----a) Microprocessor b) Memory c) Input-Output Devices d) all of these 2) is/are the example/s of ROM. a) EPROM b) MASK c) EEPROM d) all of these 3) Memory IC 2764 is of----- Byte a) 2K b) 4K c) 8 K d) 16 K 4) To interface IC 2764 with 8085, it requires ----- address lines. c) 13 a) 11 b) 12 d) 14 5) Memory IC 27128 is of ------Byte a) 2K b) 4K c) 8 K d) 16 K 6)To interface IC 27128 with 8085, it requires ----- address lines. d) 14 a) 11 b) 12 c) 13

## Q. Long answers questions:

1) Draw a block diagram of Microcomputer system and explain its various parts.

- 2) What are semiconductor memories? Explain them.

- Draw the neat schematic showing the interface between 8085 microprocessor and 2764 EPROM. Also explain memory map indicating the address and range.

- Draw the neat schematic showing the interface between 8085 microprocessor and 27128 EPROM. Also explain memory map indicating the address and range.

- 5) Interface 27128 EPROM chip to 8085 microprocessor and explain its memory map.

- 6) How 2764 EPROM chip is interfaced to 8085 microprocessor? Find its memory map.